大家听说过 IEDM 吗?

不瞒大家说,直到前两天我收到了一封广告邮件之后,才知道美国在每年的 12 月还会举行这么一个行业峰会。。。

简单来说,IEDM ( 国际电子器件大会, International Electron Devices Meeting ),被誉为半导体领域的 “ 奥林匹克盛会 ” ,会汇集业界巨头( 英特尔、台积电、三星、IBM 等 )和各大顶尖高校,坐在一起头脑风暴。

具体都风暴些啥呢?从晶体管结构、到互连材料,业界巨头和学者们不断抛出新的思路,尝试挑战物理的极限,共同指明未来半导体行业的发展方向。

也就是说,芯片未来怎么发展,很大程度上都得看这个会上都聊了啥。

既然突然撞见了,那托尼今天就带大家理理最近的 IEDM 2025 上都有哪些新方向,给大家聊聊芯片未来会怎么进化。

首先,最近两年在 IEDM 上被反复提及的一个议题是,芯片里头的导体:铜要顶不住了。

我们初中物理课上都学过,在材料、长度和温度一定时,导线的电阻与横截面积成反比,简单来说就是导线越细,电阻越大。

还是用经典的高速公路例子给大家解释,原本宽阔( 导线粗 )的路上六七辆车( 电子 )随便跑,但一旦路变窄( 导线细 )了,车( 电子 )就跑不动了。

所以芯片铜互连材料也是如此,制程越先进电阻越高,而且铜到了纳米级别之后,电子在狭窄的空间里动不动就会撞到边界、拐弯、减速,电阻会上升得比想象中快得多。

这样一来信号传输慢如蜗牛,功耗还会爆炸。

于是乎,在近几年的 IEDM 大会上,电子行业的大佬们已经开始讨论用钌金属 ( Ru )去代替现有的铜作为互连材料,而这回大家又围绕着钌金属提出了很多新的路子。

钌单质长这样

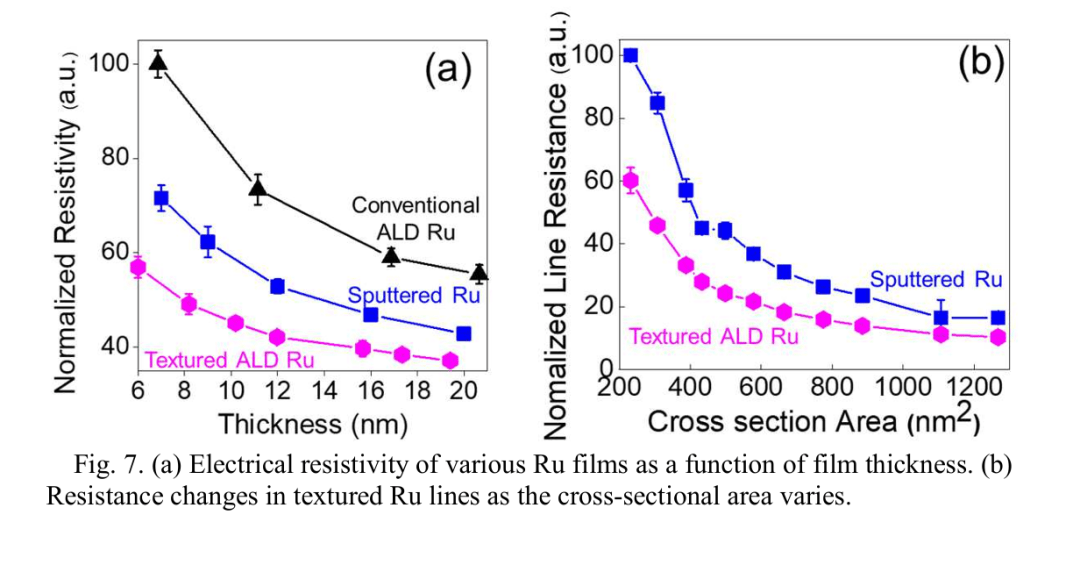

先给大家解释一下,为啥大家都看上了钌金属呢?首先是因为在极细的线宽下, 钌的电阻对 “ 变细 ” 这件事儿没那么敏感,比铜更适合做细。

其次是,钌特别适合一种叫 ALD( 原子层沉积 ) 的工艺。和传统铜互连靠 “ 往里灌再刮平 ” 的电镀工艺不同,ALD 工艺是一层一层地贴,哪怕导电沟槽极度窄和深,也能把钌均匀铺好。

最重要的一点是,这种工艺还能让钌内部的 “ 晶粒排列 ” 更整齐,电子跑起来不容易被反复打断 ——

就好比把原本坑坑洼洼、岔路很多的土路,升级成了平整的柏油路,电阻自然也就降下来了。

这不在 IEDM 2025 会上,来自三星的实验结果表明,在横截面积只有 300 nm² 的超细互连线中,采用这种工艺制造的钌线相比溅射工艺的钌线电阻降低了 46%。

而且这次 imec ( 比利时微电子研究中心 ) 还展示了在 16 nm 间距下( 可用于A7 ,即 0.7 nm 以下工艺 )实现的两层钌互连结构,并在 300 mm 晶圆上取得了 95% 以上的良率,这也说明了钌互联可能真的要来了。

解决了互连材料之后就万事大吉了么?nonono,路修好了, “ 车 ” 也得听指挥才行 ——

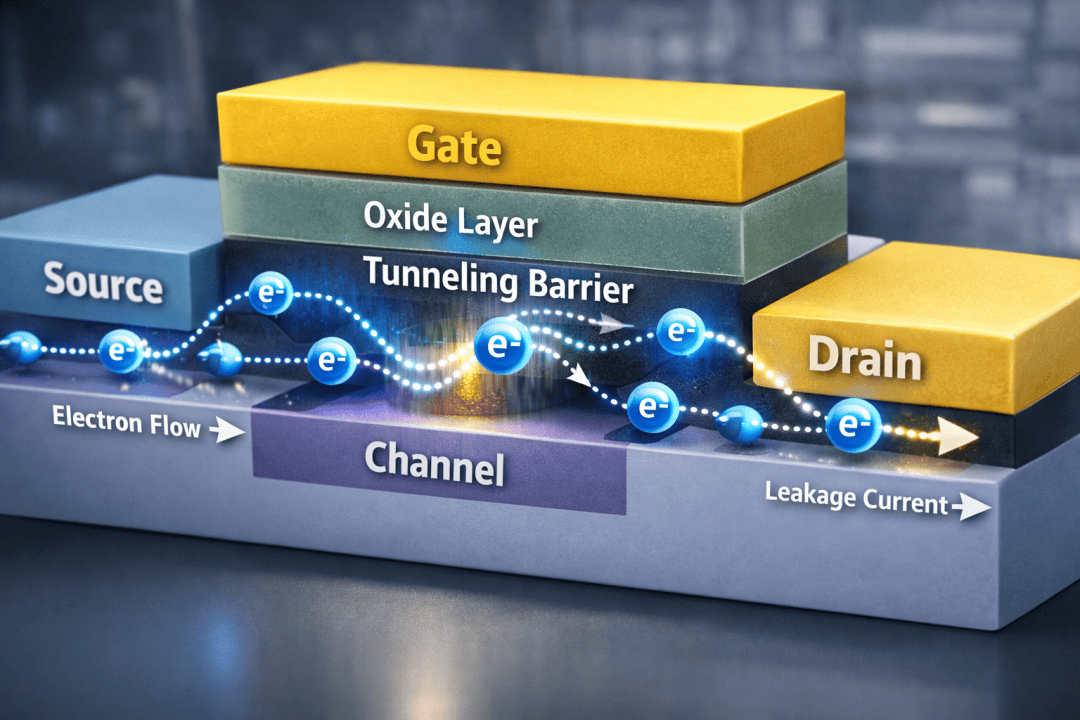

大家都知道,芯片最底层的逻辑其实就两种状态 —— 通电,或者不通电。

晶体管通过栅极( 门 )来控制电流的开与关 ( 1 和 0 )。但问题是当晶体管小到一定程度的时候,电子就开始胡来了,即便是门关上了,还是会有电子偷溜过去。

电子这样叛逆的后果是,漏电上升、静态功耗飙升、芯片发热变严重,为了温度只能降频、限功耗,性能提升反倒功耗墙卡住了,合着一来二去白忙活。

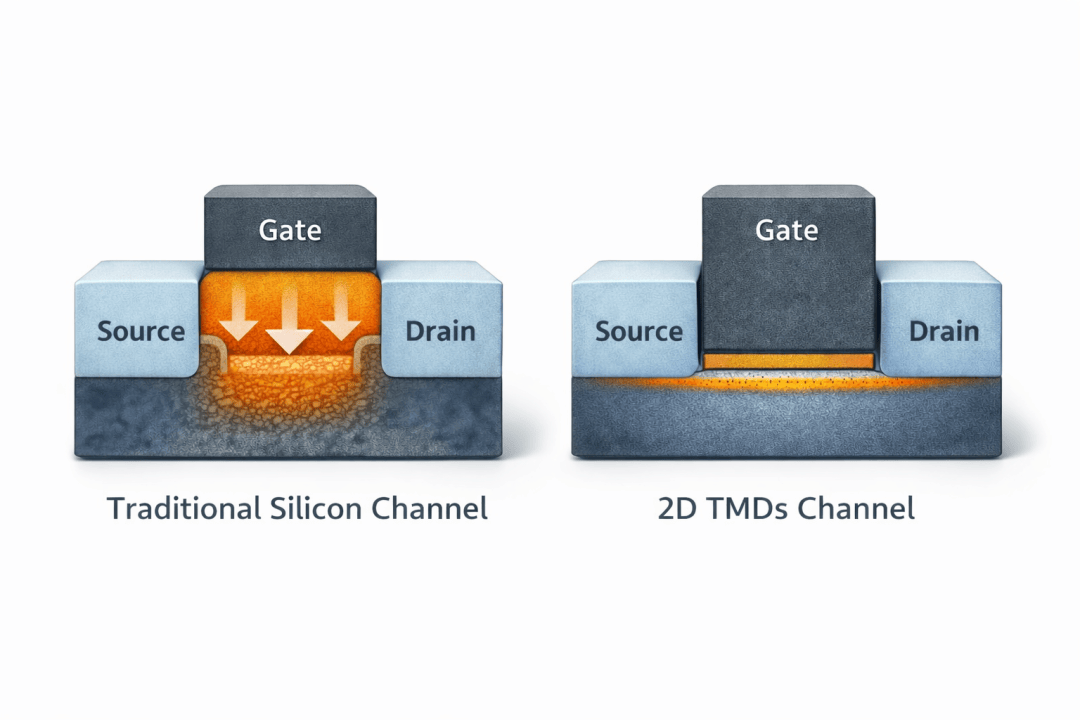

所以说 IEDM 上提到的另一个重要议题,就是用二维过渡金属硫化物( 2D TMDs )去替代原本硅的沟道材料。

托尼给大伙简单解释一下:以往的硅沟道,因为沟道它比较厚,正所谓天高皇帝远,栅极( 门 )从上面指挥,远端的路通不通它就管不住了,这底下就容易漏电。

而以硫化钼 MoS₂、硒化钨 WSe₂ 为代表的 2D TMDs 材料,厚度只有几层原子厚,栅极控制起电子就手拿把掐。

不过话说回来, 2D TMDs 相比钌互联来讲还是有点遥远,目前更多的还是在原型研究阶段。

因为 2D TMDs 材料的生长工艺容易把栅极搞坏,过于薄的材料后续也更容易翘边,还得解决低阻接触等等问题,后面要大规模量产还得再沉淀沉淀。

除了以上这两个比较新颖的知识,IEDM 还聊了一些老生常谈的话题,比如新的栅极堆叠方式,也就是门结构。

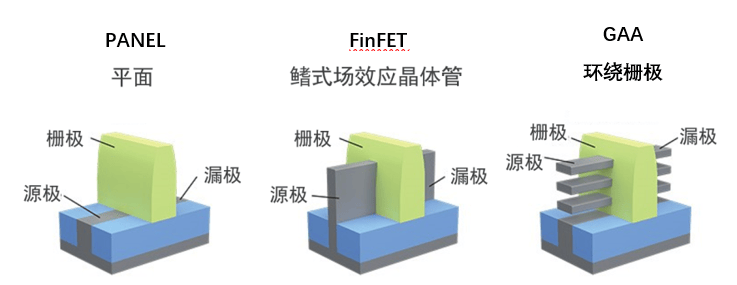

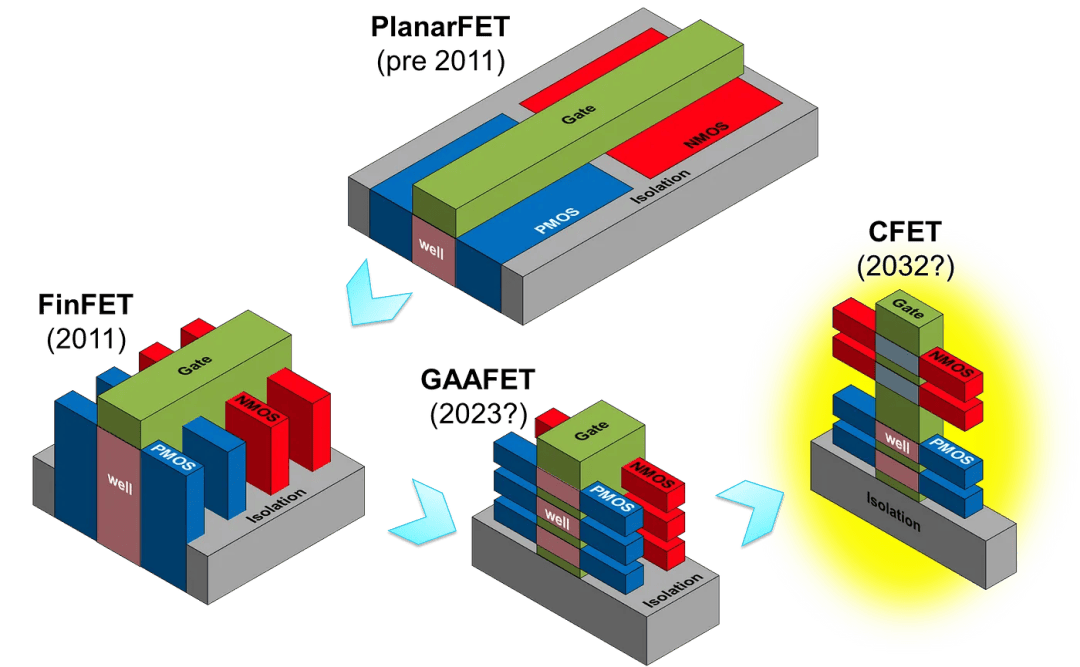

这个大家可能比较熟悉了,过去的十几年里我们从 FinFET ( 鳍式场效应晶体管 )到 2nm 工艺的主流结构 GAA( 环绕栅极 ),晶体管密度不断提高。

但在最近几年的 IEDM 上,一个被越来越频繁提起的新方向就是台积电等巨头反复押注的 CFET(互补场效应晶体管)。

相比过去的晶体管密度横向发展、在土地上建平房的方式, CFET 的思路,则更像是平地起高楼,通过垂直叠加晶体管的方式, 利用三维空间提高晶体管密度。

但是具体的我们今天就不讲了,感兴趣的小伙伴可以自己搜搜看,毕竟 AI 工具现在都这么好用了 ( doge )。

今儿个虽然给大家絮絮叨叨聊了不少,但这些技术讨论也只是 IEDM 上的冰山一角。。。

在每年的会议里,有人研究材料,有人研究工艺,也有人反复推翻自己前面的结论,再从头来过。每一篇论文背后,都有无数次失败、争论和推倒重来,凝聚着工程师们的心血。

而从更大的视角来看,微电子行业本身,就是人类不断逼近极限、又不断换路前行的缩影。也许大多数名字不会被记住,但正是这群人一次次的头脑风暴,才让整个世界一点点向前推进。

某种意义上,这就是属于电子工程师的 “ 群星闪耀时 ” 。

撰文:小柳

编辑:米罗 & 面线

美编:子曰

图片、资料来源:

techovedas.com

FAQware

维基百科

IEDM官网

粤讯

部分图片由AI生成